【48812】怎么对Spectre下的LC-VCO进行仿真验证?

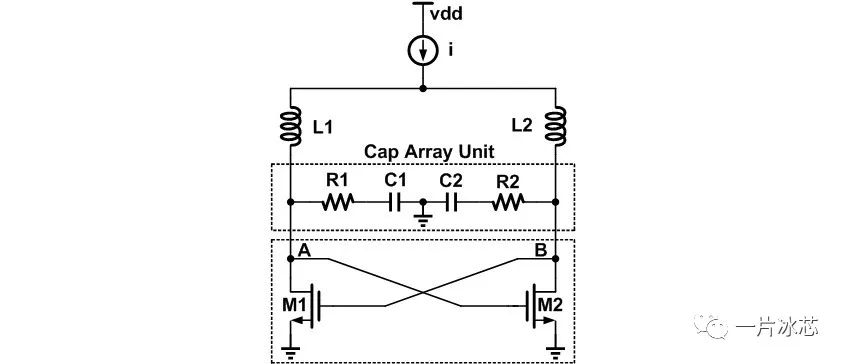

LC-VCO的等效电路如图1所示,实践使用中L1和L2由带中心抽头的对称电感组成,抽头接电流源(图中i)。

为减小Rj,vdd一般由电流源可由PMOS管完成,也可由电阻完成,两者在工程中都有使用,差异主要是低中频的闪耀噪声和热噪声及电流是否固定,详细差异今后有时机再跟我们共享。

R1、R2、C1、C2组成LC-VCO的电容阵列,其间R1、R2为MOS管的导通或关断电阻,C1、C2一般为MOM电容,电容阵列(图中Cap Array Unit)一般带有二进制权重(如1:2:4:8:16)。

交差耦合管M1、M2构成负阻用于抵消LC振动环中的寄生电阻,以保持等幅振动。为了简化剖析图1中没有画出varacor电容,varactor电容用于调整VCO的输出频率。

可经过核算或前面阻抗改换中介绍的sp仿真得到电容阵列的等效并联电阻Rpc及并联电容Cpc。图1中电感为抱负电感,感值为L1+L2,假如为非抱负电感可经过电感的S参数模型仿真出等效电感、电容、电阻,为便于剖析这儿简化成了抱负电感。

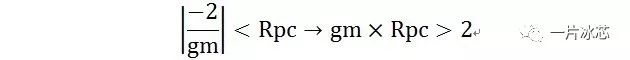

经过画小信号可得,A、B两点向下看进去的等效并联阻抗为Rpm=-2/gm,(gm1=gm2=gm),A、B两点向下看进去的等效并联电容为Cpm。为保持振动,有下式建立:

其间gm为M1或M2的跨导,Rpc为电容阵列的等效并联电阻(工程中还要与电感和varactor电容的等效并联电阻进行并联)。

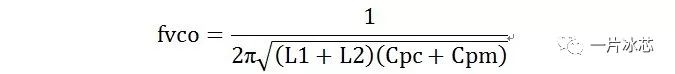

Rpc、Rpm及gm只影响起振及振动起伏,振动频率只取决于L1、L2、Cpc、Cpm。

注:仿线的等效并联电阻及电容时,应给A、B两点合理的共模电压,由于共模电压会影响并联阻抗;假如A、B两点振动起伏较大,使得M1和M2管处于大信号状况小信号sp仿真将不再适用,应选用pss+psp进行大信号仿真。

声明:本文内容及配图由入驻作者编撰或许入驻协作网站授权转载。文章观念仅代表作者自己,不代表电子发烧友网态度。文章及其配图仅供工程师学习之用,如有内容侵权或许其他违规问题,请联络本站处理。告发投诉

(SMIC0.18 RF CMOS库)。可是自己研讨了良久也不出振动波形,跟着 试验指导书一步一步去做也不对,各个器材的参数也是依照指导书来的,

设置进程,画出gm/ID--ID/W等曲线,并导出gm/ID--ID/W数据到Excel表。

pcb板的功能,我将pcb的参数提取出来后,用sigrity导出了s参数网络及spice模型1,在用Analoglib中的nport导入s参数

啊,库里就一个电容能选的,也没有电感能够选。(由于课程供给的工艺库就只有这个350nm的,想做

窗口不能全屏设置,点击全屏按钮,窗口尽管全屏了,但有用显现区域仍是那么小,不知道怎么设置,谁遇到过相同的状况,费事奉告一

办法以及实例工程文件 /

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今天宣告,SK hynix Inc. 已布置 Cadence®

器,用于对其面向 PC 和移动使用的 DDR4 和 DDR5 DRAM

反常—薛定谔的NetlistInclude /

驱动LSM6DS3TR-C完成高效运动检测与数据收集(10)----交融磁力计进行姿势解算

2024年上海海思MCU开发者体会官招募,手机/MatePad大奖等你拿!

时间: 2024-08-04

时间: 2024-08-04  作者:

作者: